孕龍LAP-C-322000 邏輯分析儀 (32通道/200MHz時序/每通道2M bits記憶體,

產品型號 : LAP-C-322000

Zeroplus(孕龍科技)322000是一款USB外接式PC-Based介面邏輯分析儀, 具備32通道, 每通道2M bits深度記憶體(總共64M bits), 最高每通道200MHz 取樣率(Timing/非同步)及100MHz 狀態(State/同步)輸入. 免費提供I2C,CAN,SPI, UART,RS232等數十種匯流排解碼(decode)功能

| 具有外部按鈕執行邏輯分析儀取樣功能 |

| 在孕龍邏輯分析儀的硬體上,有一個START的按鈕,當邏輯分析儀軟體在開啟的狀態,可利用此按鈕來讓邏輯分析儀執行取樣的動作。此按鈕能讓您更快速的操作邏輯分析儀取得被測物的資料。 |

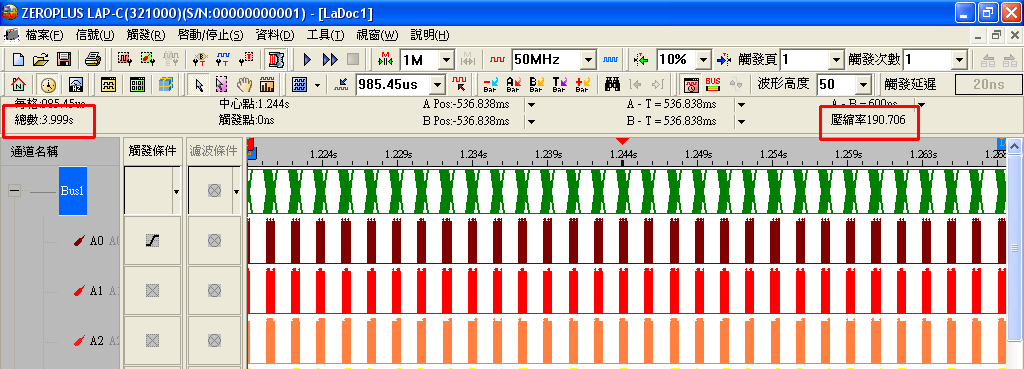

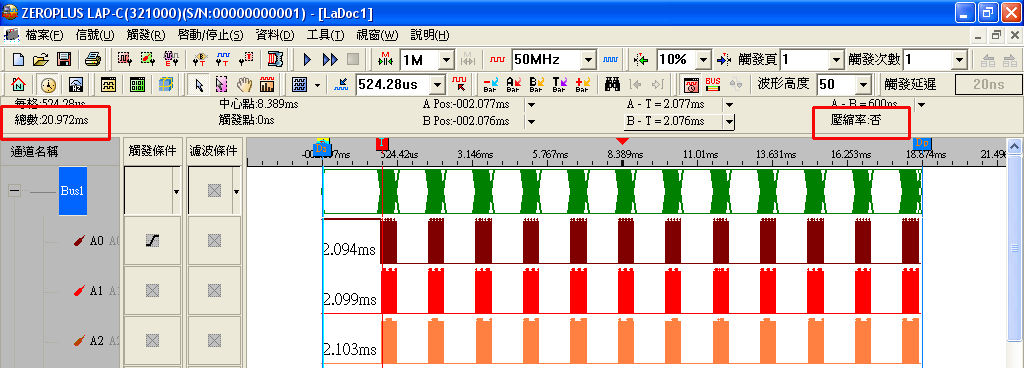

| 壓縮技術 |

|

|

||

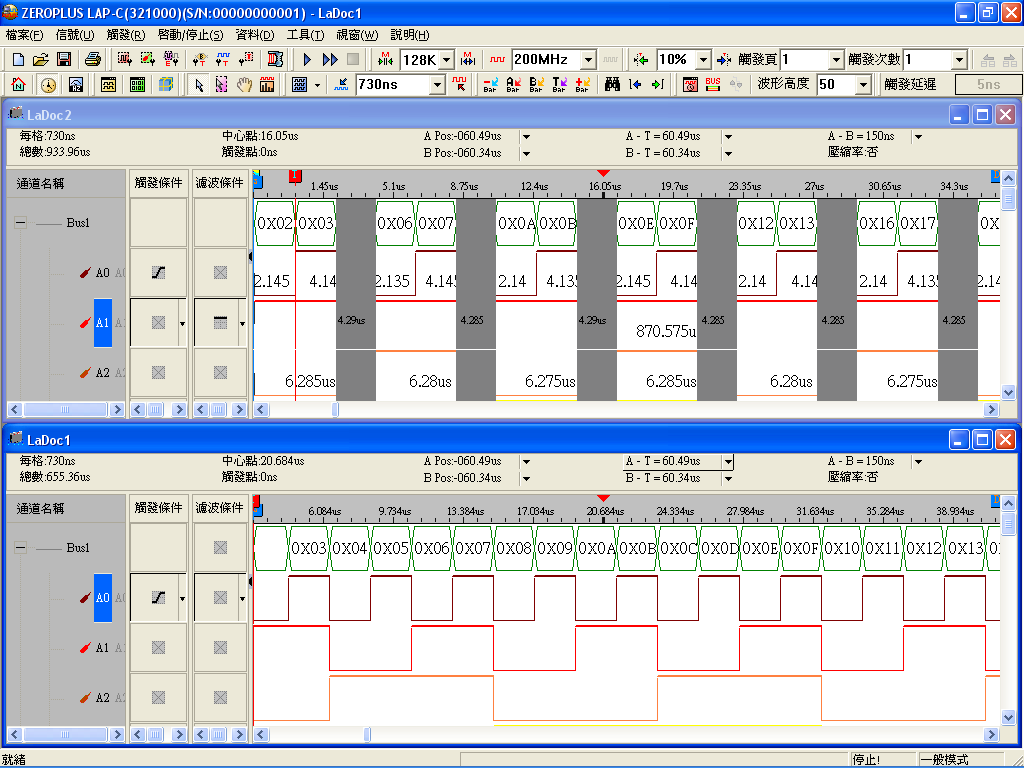

| 孕龍科技推出波行壓縮專利技術,可以在不增加記憶體的狀況下獲取更長的波形資料。For Example:設定記憶體深度為1M,取樣率為50MHz。未開啟壓縮功能時僅可擷取20.972ms,若開啟壓縮功能後,以同樣記憶深度為1M,取樣率為50MHz進行取樣,則可以將波形時間增加至3.999s,大大的提升了擷取資料量。 | |||

| 信號濾波延遲 |

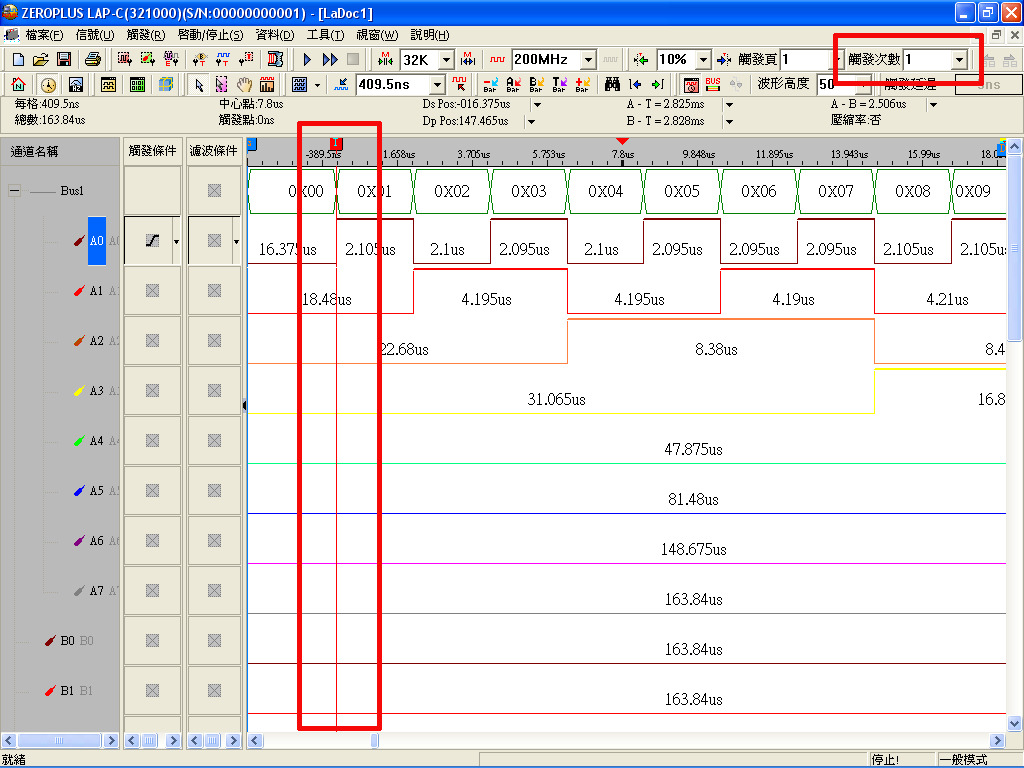

| 觸發分頁技術 |

| 觸發次數計算 |

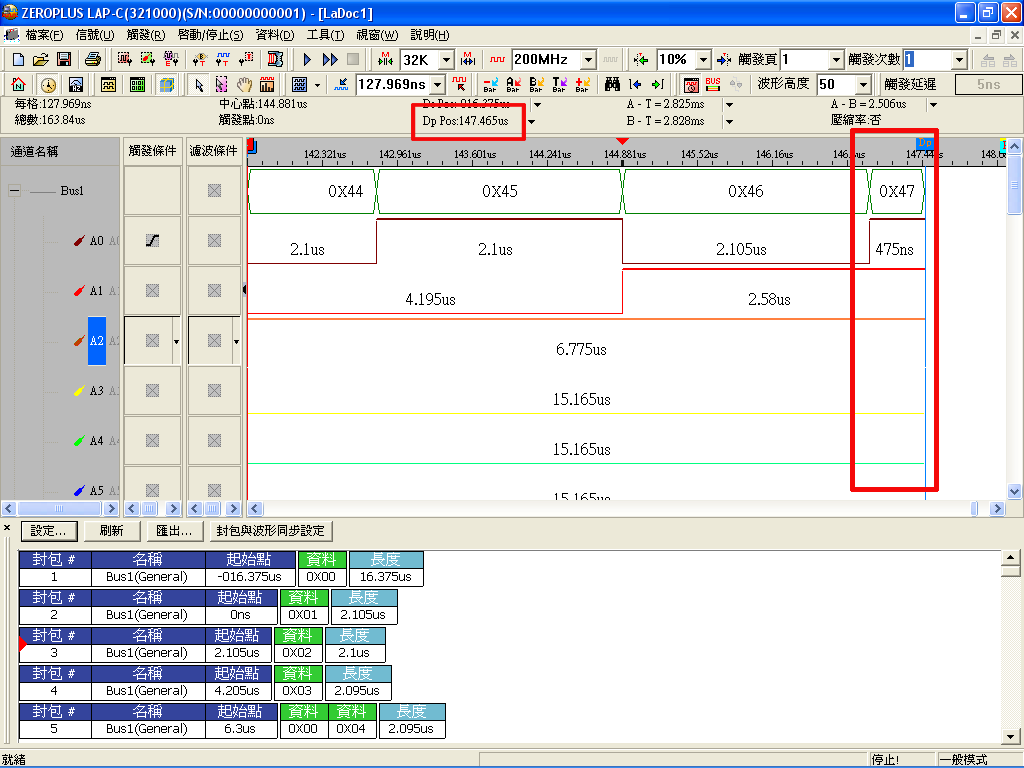

| 記憶體分析 |

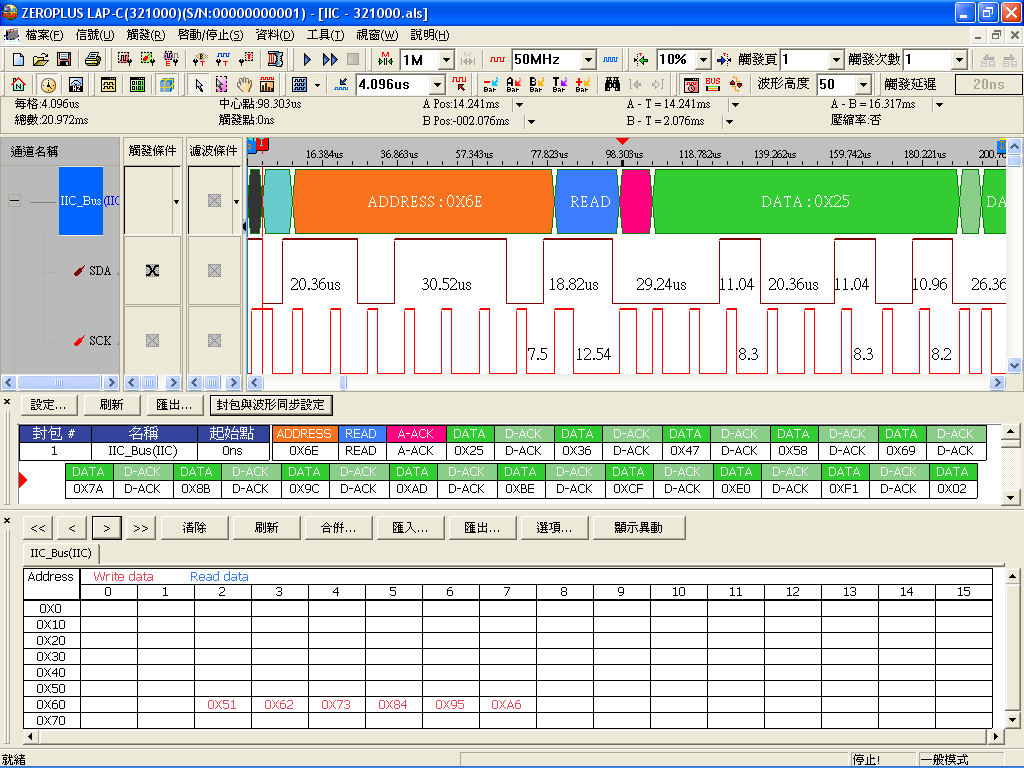

|

|||

| 孕龍邏輯分析儀加入了記憶體分析功能(Memory Analyzer),針對匯流排中有使用ADDRESS的類別,如IIC、HDQ、3-WIRE、PM、SM、IIC(EEPROM 24LX)…等等,能夠將匯流排中的ADDRESS、READ/WRITE、DATA狀態記錄於記憶體分析表中,讓使用者進行匯流排分析時也能夠針對ADDRESS、READ/WRITE、DATA加以記錄分析。 | |||

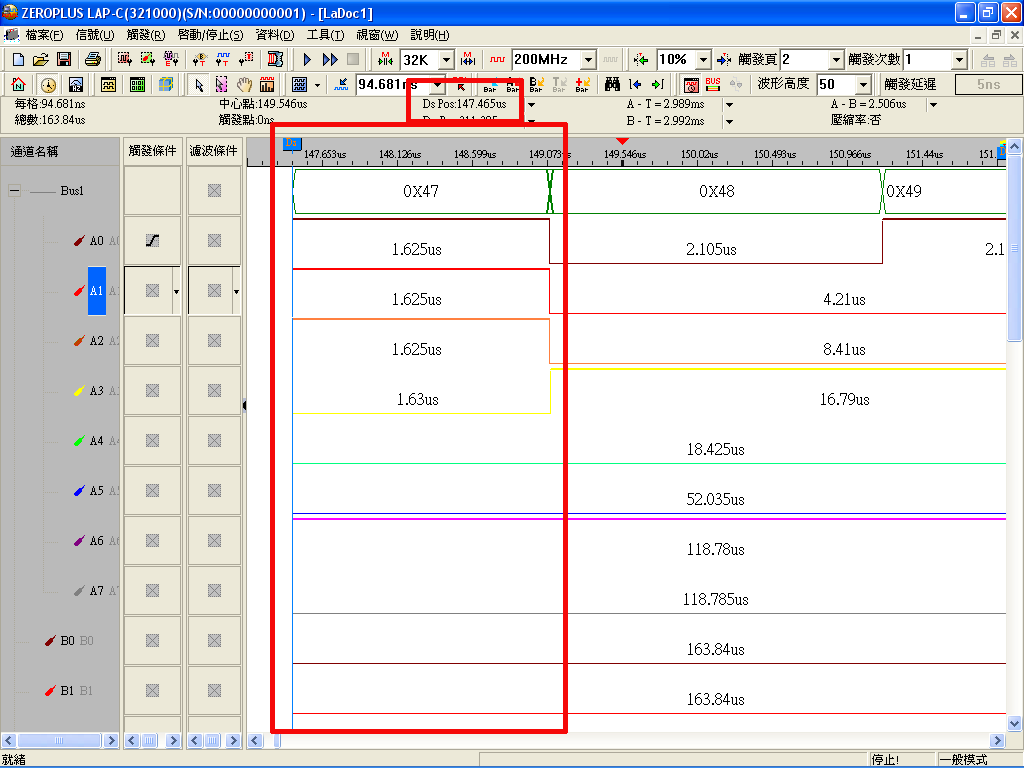

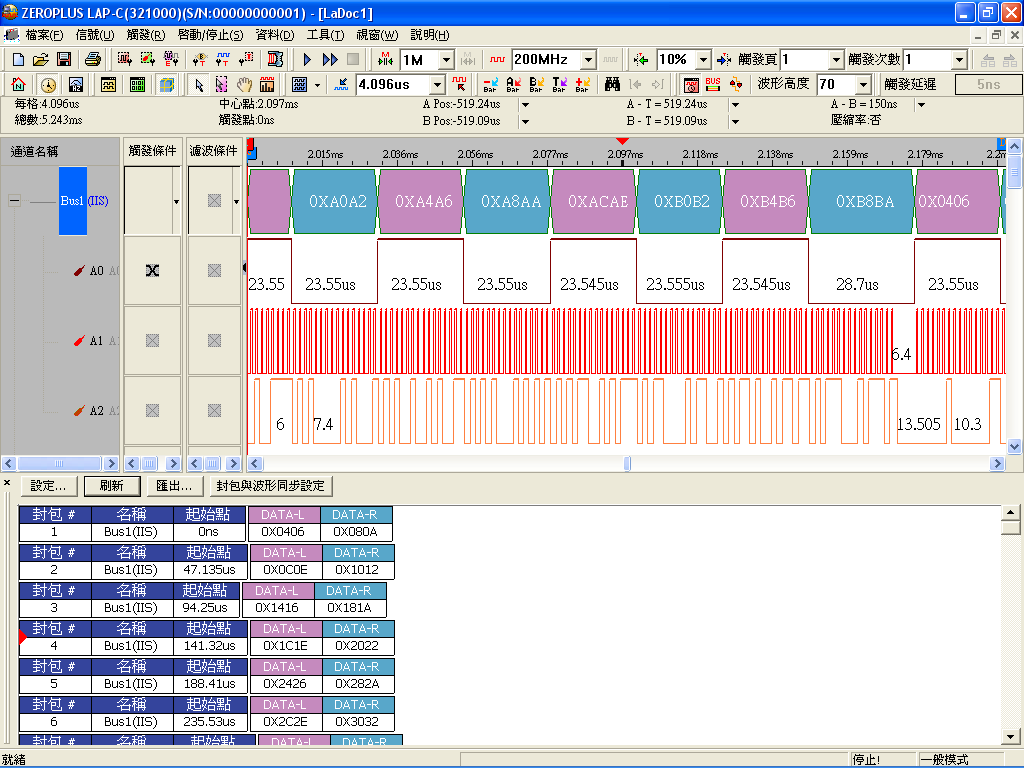

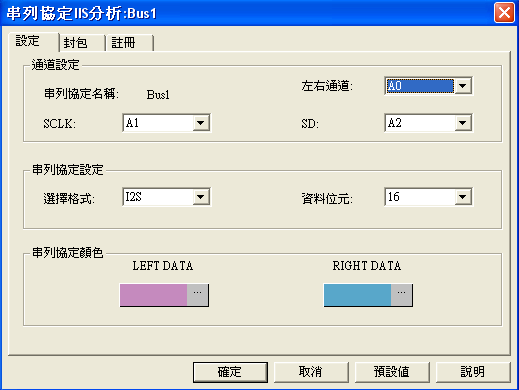

| 匯流排協定分析實例 – IIS匯流排協定分析解碼 |

|

|

||

| 孕龍科技的IIS匯流排分析模組,可幫助使用者進行IIS匯流排分析,透過解碼模組可將訊號中的Data-L及Data-R數值直接顯示於螢幕上,孕龍科技IIS匯流排分析模組可依照待測IIS訊號格式讓使用者選擇Data bit長度為16、20、24、32 bits,方便使用者面對各種不同的IIS訊號均能順利分析。 | |||

| 產品型號 | LAP-C (322000) | |

| 支援系統 | Windows 2000 / XP / Vista / Win 7 | |

| 傳輸介面 | USB2.0 (1.1) | |

| 通道數 | 32 | |

| 取樣頻率 | 內部(時序)(非同步) | 100Hz ~ 200MHz |

| 外部(狀態)(同步) | 100MHz | |

| 待測信號 | 頻寬 | 75MHz |

| 觸發電壓範圍 | -6V~+6V | |

| 觸發電壓解析度 | ±0.1V | |

| 記憶體 | 記憶體容量 | 64Mbits |

| 每通道記憶體深度 | 2Mbits | |

| 每通道波形資料壓縮 | 硬體壓縮最高256倍 | |

| 觸 發 | 觸發方式 | Pattern/Edge |

| 觸發通道 | 32 CH | |

| 觸發延遲 | YES | |

| 觸發階層 | 1 階 | |

| 觸發計數 | 1~65535 | |

| 時基範圍 | 5ps~10Ms | |

| 波形垂直縮放比例 | 1~5.5 | |

| 操作介面語言 | 中文(簡體/繁體) / 英文 | |

| 波形觸發分頁最大值 | 8192頁 | |

| 脈波寬度觸發模組 | 隨主機贈送 | |

| 相位誤差 | < 1.5ns | |

| 電 源 | 電源 | USB供電 (DC 5V, 500mA) |

| 靜態消耗功率 | 1W | |

| 瞬間最大消耗功率 | 2W | |

| 最大輸入電壓 | ±30V | |

| 輸入阻抗 | 500KΩ/10pF | |

| 安規認證 | FCC / CE / WEEE / RoHS / REACH | |

| 產品體積 | 125mm x 92mm x 25mm | |

| 標準配備 | 測試線 | 16 pin * 1 / 8 pin * 2 / 2 pin * 1 / 1 pin * 1 |

| 測試鉤 | 36 支/包 | |

| USB線 | 1 | |

| 安裝光碟 | 1 | |

| 快速安裝手冊 | 1 | |

| 攜帶包 | 1 | |